Product Summary

The MPC8545HXATG is a powerQUICC III integrated processor. It features one Serializer/Deserializer (SerDes) interface to be used for high-speed serial interconnect applications. The SerDes interface can be used for PCI Express and/or serial RapidIO data transfers. The MPC8545HXATG is currently targeted to these specifications. Some of these specifications are independent of the I/O cell, but are included for a more complete reference. These are not purely I/O buffer design specifications.

Parametrics

MPC8545HXATG absolute maximum ratings: (1)Core supply voltage, VDD: -0.3 to 1.21V; (2)PLL supply voltage, AVDD: -0.3 to 1.21V; (3)Core power supply for SerDes transceivers, SVDD -0.3 to 1.21V; (4)Pad power supply for SerDes transceivers, XVDD -0.3 to 1.21V; (5)DDR and DDR2 DRAM I/O voltage, GVDD: -0.3 to 2.75V; (6)PCI/PCI-X, DUART, system control and power management, I2C, Ethernet MII management, and JTAG I/O voltage, OVDD: -0.3 to 3.63V; (7)Local bus I/O voltage, BVDD: -0.3 to 3.63V; (8)DDR/DDR2 DRAM signals, MVIN: -0.3 to (GVDD + 0.3)V; (9)DDR/DDR2 DRAM reference, MVREF: -0.3 to (GVDD/2 + 0.3)V; (10)Three-speed Ethernet I/O signals, LVIN: -0.3 to (LVDD + 0.3); (11)Local bus signals, BVIN: -0.3 to (BVDD + 0.3); (12)DUART, SYSCLK, system control and power management, I2C, Ethernet MII management, and JTAG signals, OVIN: -0.3 to (OVDD + 0.3)V; (13)PCI/PCI-X, OVIN: -0.3 to (OVDD + 0.3)V; (14)Storage temperature range, TSTG: -55 to 150°C.

Features

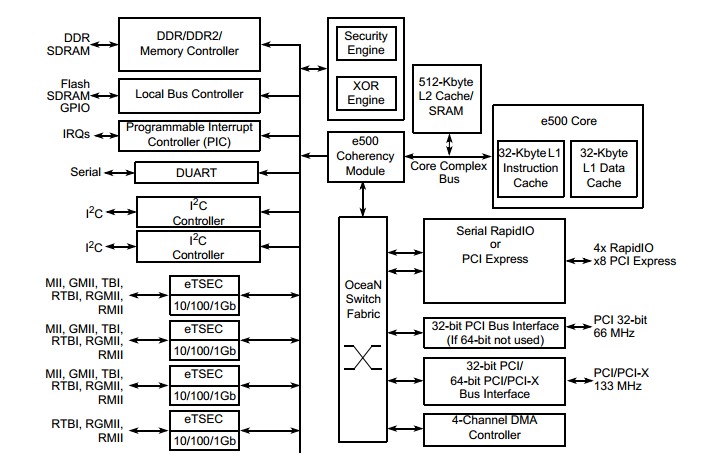

MPC8545HXATG features: (1)High-performance 32-bit core built on power architecture technology; (2)512-Kbyte L2 cache/SRAM; (3)Address translation and mapping unit(ATMU); (4)DDR/DDR2 memory controller; (5)Programmable interrupt controller(PIC); (6)Integrated security engine(SEC) optimized to process all the algorithms associated with IPSec, IKE, WTLS/WAY, SSL/TLS, and 3GPP; (7)Dual I2C controllers; (8)Boot sequencer; (9)DUART; (10)Local bus controller(LBC); (11)Four enhanced three-speed Ethernet controllers(eTSECs); (12)OCeaN switch fabric; (13)Integrated DMA controller; (14)Two PCI/PCI-X controllors; (15)Serial RapidIOTM interface unit; (16)RapidIO-compatible message unit; (17)PCI Express initerface; (18)Pin multiplexing for the high-speed I/O interfaces supports one of the following configurations: 8 PCI Express, 4 PCI Express and 4 serial RapidIO; (19)System performance monitor; (20)System access port; (21)JTAG boundary scan, designed to comply with IEEE Std. 1149.1TM.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|---|---|---|---|---|---|---|---|---|---|---|

|

MPC8545HXATG |

Freescale Semiconductor |

Microprocessors (MPU) PQ38 8548 |

Data Sheet |

Negotiable |

|

||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|

MPC800 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

MPC801 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

MPC801KG |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

mPC8104GR |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

mPC8106TB |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

mPC8109TB |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))